phy usb что это

PHY в сетевых картах, характеристиках и функциях

PHY это очень распространенный термин, когда речь идет о сетей и действительно, даже если вы никогда не слышали этого раньше, это то, что ваш сетевая карта есть, даже тот, который интегрирован с материнская плата. Это довольно важный компонент, поэтому в этой статье мы собираемся объяснить, что это такое, что это такое. для и вообще все что ты должен знать об этом.

Обычно, когда речь идет о PHY, это обычно делается в сочетании с сетевым контроллером, который, конечно, является частью сетевой карты. Сегодня он есть у всех сетевых карт, в том числе на материнских платах. Итак, давайте посмотрим, что это такое и что он делает.

Что такое PHY?

Устройство PHY обычно включает в себя дополнительный уровень кодирования, называемый PCS (подуровень физического кодирования), и уровень, зависящий от физической среды (PDM), который кодирует и декодирует данные, которые передаются и принимаются.

Типы и примеры использования

В начале мы говорили вам, что все сетевые карты имеют PHY, но реальность такова, что это только в том случае, если у них есть физические разъемы (вы можете подумать, что было бы абсурдно не иметь их, но в профессиональной среде там есть). являются сетевыми контроллерами, которые не имеют PHY, потому что их функция заключается в управлении другими сетевыми картами, поэтому у вас нет своих собственных разъемов).

A_D Electronics

development and research

Выбор стандартного интерфейса для обмена данными

В этой заметке будет краткий обзор различных распространённых интерфейсов, которые используются в качестве канала обмена данными между персональным компьютером (ПК) и разрабатываемым\проектируемым устройством (или в пределах устройств только). Заметка, скорее, для начинающих схемотехников \ программистов, которая поможет определиться с начальным выбором, оценив возможности и ограничения описанных интерфейсов.

Заметка не претендует на полноту изложения или обстоятельный подход к каждому интерфейсу, могут быть ошибки или неточности, это скорее заметка с авторскими пометками и моё мнение может не совпадать с вашим. 🙂 Если интересно — прошу под кат:

Краткое сравнение

Плюсы и минусы каждого интерфейса в виде таблицы для наглядности:

Чуть подробнее

Virtual COM (USB-to-UART) — это, конечно, уже древний вариант, но для сравнения я решил добавить и его. USB-to-UART порт можно организовать и на МК со встроенным USB PHY, есть куча примеров как от производителей МК, так и от любителей. Если же требуется внешний чип, то в качестве примера наиболее распространённые микросхемы:

USB 2.0 — вполне рядовое решение для большинства задач с достаточно низкими потоками данных. Существует 3 режима работы, отличающиеся скоростью передачи:

Для первых двух зачастую не требуется никаких внешних микросхем, и USB PHY уже содержится в МК\SoC даже начального уровня (к примеру, в STM32F042F6P6 внутри есть даже точный тактовый генератор на 48 МГц, что освобождает от необходимости установки внешнего кварца и поддержка USB 2.0 Full-speed на борту!), чего хватит для большинства задач по управлению или для задач с небольшими потоками данных.

Для High-speed режима работы в большинстве случаев уже потребуется внешний PHY, с которым МК будет взаимодействовать по интерфейсу ULPI или UTMI. Возможные PHY с поддержкой High-speed:

USB 3.0 (3.1 Gen 1) — первая версия USB с режимом работы SuperSpeed и теоретической скоростью передачи данных в 5.0 Гбит/с, реальная же скорость передачи будет ощутимо ниже (к примеру, можно почитать тест производительности от FTDI на FT600\FT601). Потребуется внешний PHY, а также имеются повышенные требования при проектировании схемы и разводке ПП. На самом деле возможны 2 варианта реализации:

Второй вариант, конечно, очень гибкий, но потребует ощутимых трудозатрат для реализации (особенно если не покупать готовое IP ядро), первый же подойдет для быстрого старта с хорошими примерами от производителей, в качестве примера самые распространённые МС:

USB 3.1 Gen 2 (Type C) — следующее поколение USB с режимом работы SuperSpeed+ и теоретической скоростью передачи данных в 10.0 Гбит/с. Реализуется способом, когда скоростные линии USB 3.1 идут к LVDS трансиверам ПЛИС через сереализатор (2 * LVDS 10 Гбит/с разделяется на 4 * LVDS 5 Гбит/с, которые уже и идут в USB Type C, приём\передача по 2 линии) и установлен внешний USB 2.0 PHY для начальной инициализации USB. В качестве примера IP ядро для реализации USB 3.1:

А в качестве примера реализации схемотехники USB 3.1 Gen 2 советую посмотреть Intel Cyclone 10 GX FPGA Development Kit.

USB 3.2 — будущее поколение со скоростью до 20 Гбит/с (2 линии по 10 Гбит/с), спецификации можно почитать на USB.ORG. Реальных устройств пока нет.

PCI Express — это уже компьютерная шина с последовательной передачей данных, по факту передача идёт на 1\4\8\12\16\32 двунаправленных линиях, а линия, в свою очередь, состоит из двух LVDS, на приём и передачу. Пропускная способность для существующих устройств с PCI Express (на момент написания) в зависимости от количества линий и версии:

Более подробно можно почитать на Википедии. Если говорить о наиболее реализуемых вариантах на ПЛИС или ASIC, то вкратце это выглядит так:

В качестве примера реализации схемотехники PCI Express х4 советую посмотреть Intel Cyclone 10 GX FPGA Development Kit.

Варианты от разных компаний внешних PHY для реализации PCI Express с пометкой количества линий:

Thunderbolt — аппаратный интерфейс, ранее известный как Light Peak. Интерфейс был разработан компанией Intel в сотрудничестве с Apple для подключения периферийных устройств к ПК (маку) и схож с USB Type C. Может комбинировать в себе PCI Express и DisplayPort. Скорость передачи данных до 10 Гбит/с по проводному кабелю и до 20 Гбит/с при использовании оптического кабеля. Применять в случае изготовления устройств исключительно для Apple продукции, в любом другом случае это будет провал и бесполезная трата времени и ресурсов.

Ethernet — универсальное решение. Крайне легко объединять устройства в сеть, добавлять в существующую дома\работе сеть, обмениваться с ними данными (примеров более чем достаточно, как со стороны ПК, так и со стороны МК\ПЛИС\SoC) и не париться о гальванической развязке между устройством (-ами) и ПК.

В навороченных SoC, МК бывает встроенный PHY, в случае создания устройства на средне-бюджетных МК или ПЛИС уже не обойтись без внешнего PHY. В качестве примера немного различных PHY с разными интерфейсами подключения и скоростями:

В качестве примера внешние PHY (так-то корзинку-держатель для оптического модуля можно подключить напрямую к ПЛИС, и из дополнительных элементов потребуются разве что 6 резисторов да фильтры по питанию и развязочные конденсаторы на дифференциальные линии LVDS):

Wi-Fi — этот вариант подходит для малогабаритных или\и портативных устройств, когда требуется применение стандартного интерфейса для связи, максимальное удобство, а также нет жестких требований на задержки и объемы потока данных (к примеру, вы делаете автономное устройство, которое периодически управляется по сети или имеет WEB для удобной работы с ним как с ПК, так и с планшета\телефона). Также стоит отметить, что как таковых Wi-Fi PHY обычно не ставят, Wi-Fi PHY уже идет в составе с каким либо АРМ-ом зачастую (Wi-Fi SoC), что упрощает схемотехнику вашего устройства и положительно влияет на габариты и цену.

В качестве примера различные WiFi SoC:

Также стоит отметить и альтернативный вариант использования этого интерфейса в случае применения одноплатных ПК на Linux, примеры одноплатных ПК на «больших АРМ-ах»:

Bluetooth — это вариант для ультра малопотребляющих устройств, с повторяющий во многом Wi-Fi вариант исполнения, но с еще худшей пропускной способностью и еще большими задержками, но стоит отметить, что есть узконаправленные типы Bluetooth устройств, к примеру аудиоприёмники\передатчики, которые идеально заточены на потоковую передачу именно звука вкупе с максимально низким потреблением. Так что склонение к выбору именно этого интерфейса сильно зависит от решаемой задачи, так как этот вариант крайне специфичен и ограничен. В качестве примера различные Bluetooth SoC:

Вывод

В итоге можно сказать следующее. Стоит выбирать интерфейс исходя из 4-х основных факторов:

Отобрав большинство интерфейсов (и доступных PHY) по первым двум факторам, окончательный выбор будут определять оставшиеся два, они довольно тесно связаны как между собой, так и с вашими умениями и поставленной задачей: финальный выбор зачастую довольно сложен и зависит от совокупности вашего опыта, итоговой цели, доступного времени на изучение и разработку, доступных материалов и примеров, а также найденных проблем (что тоже немаловажно, т. к. лучше посмотреть заранее Errata и форумы хотя бы бегло, чем потом самому искать баги и почему оно не работает-то!) при работе с этим интерфейсом или даже конкретными PHY для него.

А далее уже только опыт… 🙂 На этом всё, удачи в разработках!

Русские Блоги

Один из Ethernet (Ethernet) Детальный MAC, MII, PHY

структура

Что такое MAC

Что такое MII

Для этого раздела, пожалуйста, обратитесь к разделу 22.3 Характеристики синхронизации сигнала стандарта IEEE Ethernet 802.3, который содержит более подробный контент, такой как тактовые сигналы.

RMII(Reduced Media Independant Interface)

GMII(Gigabit MII)

Что такое PHY

Регистр PHY соответствует стандарту IEEE802.322.2.4 Management functions В этом разделе есть введение, но не во всех регистрах. Отдельные регистры нужно видеть в других главах. Конечно, в документе также упоминается, где найти какой регистр.

PHY зарегистрироваться

Адресное пространство регистра PHY составляет 5 битов, и максимум 0 регистров могут быть определены от 0 до 31 (поскольку функции чипа продолжают увеличиваться, многие чипы PHY используют технологию разбиения на страницы для расширения адресного пространства, чтобы определить больше регистров), IEEE802.3 определяет Функции 16 регистров с адресами 0-15 и регистров с адресами 16-31 оставлены на усмотрение производителя микросхемы, как показано в следующей таблице.

(1) Для официального введения, пожалуйста, обратитесь к стандарту IEEE802.322.2.4 Management functions Раздел.

(2) B и E на рисунке выше указывают, является ли регистр базовым или расширенным для определенного интерфейса. Например, только интерфейсы 0 и 1 являются базовыми для интерфейса MII, а остальные расширяются.Примечание: все расширения относятся к функциям расширения, зарезервированным для будущего IEEE, а не для производителей PHY. Производители PHY могут настраивать только регистры 16

31.

(3) В стандартных документах IEEE и некоторых руководствах по PHY используются биты регистра X.y Указывает, например, 0,15, указывает 15-й бит 0-го регистра.

Control Register (Register 0)

Регистр 0 является регистром управления PHY. Основное рабочее состояние PHY может быть установлено через регистр управления. Значение по умолчанию для каждого бита регистра управления должно быть гарантировано, чтобы исходное состояние PHY при включении питания или сбросе было нормальным рабочим состоянием без вмешательства администратора. Ниже приведены функции, выполняемые каждым из контрольного регистра.

(1) Как правило, когда вы хотите изменить режим работы порта (например, скорость, дуплекс, управление потоком или информацию о переговорах и т. Д.), Вам необходимо сбросить PHY через бит сброса, чтобы конфигурация вступила в силу после установки соответствующего регистра.

(2) Значение этого бита по умолчанию равно 0.

(1) Следует отметить, что во многих случаях порт может подключиться после того, как PHY установит Loopback, и MAC не сможет отправлять кадры в порт. В этом случае вам нужно настроить Force Link на порт, чтобы использовать функцию Loopback.

(2) Значение этого бита по умолчанию равно 0.

Если PHY сообщает, что он не может работать на всех скоростях через биты 1.15: 9 и 15.15: 12, значения битов 0.6 и 0.13 должны соответствовать скоростям, на которых может работать PHY. И любая попытка установить этот бит на недопустимый будет игнорироваться.

(1) Для измененных настроек выбора скорости часто необходимо сбросить порт, чтобы конфигурация вступила в силу. Поэтому при настройке этой позиции необходимо проверить настройку автосогласования и сбросить порт через бит 15.

(2) Значения по умолчанию для битов 0,6 и 0,13 представляют собой комбинации кодирования с самой высокой скоростью передачи данных ***, которые PHY может работать в соответствии с битами 1.15: 9 и 15.15: 12.

Следует отметить, что для интерфейса 1000BASE-T автоматическое согласование должно быть включено.

(1) Режим выключения питания обычно используется, когда программное обеспечение отключает порт.Обратите внимание, что порт восстанавливается из режима выключения питания, и порт должен быть сброшен для обеспечения надежного подключения порта.

(2) Значение этого бита по умолчанию равно 0.

(1) IEEE802.3 не регулирует состояние интерфейса MDI во время изоляции, и терминал MDI может все еще работать нормально в это время. Изолят не используется в практических применениях.

(2) Поскольку многие из 100-мегабитных микросхем PHY в настоящее время имеют основной MAC-интерфейс SMII / S3MII, 8-портовый интерфейс взаимосвязан, и настройка одного порта для Isolate может повлиять на другие Нормальное использование порта, поэтому будьте осторожны, чтобы не изменять состояние bit10 по желанию.

Как правило, после изменения информации о возможностях автосогласования порта установите бит 9 на 1, чтобы перезапустить автосогласование, чтобы порт установил соединение в соответствии с новой конфигурацией.

Если PHY сообщает, что он может работать только в одном дуплексном режиме через биты 1.15: 9 и 15.15: 12, значение бита 0.8 должно соответствовать режиму, в котором может работать PHY, и любая попытка изменить бит 0.8 на недопустимый означает Следует игнорировать.

Модифицированная конфигурация дуплексного режима также должна сбросить порт для вступления в силу.

Status register

Регистр 1 является регистром состояния PHY, который в основном содержит информацию о состоянии PHY. Значение большинства битов определяется изготовителем микросхемы. Функция каждого бита подробно описана в таблице 3.

Подробное описание каждого в реестре выглядит следующим образом:

Во время отладки и обработки аномальных сбоев состояние этого битового регистра можно использовать для оценки успешности AN, чтобы дополнительно проверить, правильны ли настройки, связанные с AN, или нормальная функция AN чипа.

PHY Identifier Register

Auto-Negotiation Advertisement Register (Register 4) (R/W)

Регистр 4 является регистром уведомлений о возможности автоматического согласования. При условии включения AN (см. Регистр 0) порт будет уведомлять MDI об информации автоматического согласования через FLP согласно соответствующей конфигурации этого регистра. Когда AN сконфигурирован в состоянии Disable, конфигурация регистра 4 не будет иметь никакого эффекта, и режим работы порта определяется конфигурацией в регистре управления.

Этот регистр содержит рекламные возможности PHY, которые будут переданы партнеру по ссылке во время автосогласования. Битовое определение базовой страницы определено в стандарте IEEE 28.2.1.2. При включении питания перед началом автосогласования этот регистр должен иметь следующую конфигурацию по умолчанию:

Кодовое кодовое слово ссылки (базовое кодовое слово ссылки)

Кодовое слово базовой ссылки (базовая страница), передаваемое в пакете FLP, должно передавать код, показанный на рисунке 28-7. Функция автосогласования может использовать функцию следующей страницы для поддержки других страниц. Кодирование кодового слова ссылки, используемого при обмене следующей страницей, определено в 28.2.3.4. В пакете FLP D0 должен быть первым переданным битом.

Next Page function

Функция следующей страницы использует стандартный механизм арбитража с автоматическим согласованием, позволяющий обмениваться произвольными данными. Данные переносятся необязательной следующей страницей информации, которая следует за процессом передачи и подтверждения для кодового слова основной ссылки. Определены четыре типа кодов следующей страницы: страницы сообщений, неформатированные страницы, расширенные страницы сообщений и расширенные неформатированные страницы.

Для этой части см. стандарт IEEE28.2.3.4 Next Page function。

В стандарте IEEE все части регистра объявлений автосогласования представлены в отдельных главах. детали следующим образом:

Auto-Negotiation Link Partner ability register (Register 5) (RO)

Регистр 5 сохраняет возможности порта, объявленные одноранговым PHY, полученным локальным PHY.Структура регистра 5 в основном такая же, как и в регистре 4.

Auto-Negotiation Expansion Register (Register 6) (RO)

Регистр 6 содержит аномальную информацию процесса автосогласования PHY. Из этого хранилища мы можем узнать, поддерживает ли Link Partner автоматическое согласование и получена ли информация об автоматическом согласовании на следующей странице.

Auto-Negotiation Next Page transmit register (Register 7) (R/W)

Автосогласование регистр отправки следующей страницы содержит кодовое слово ссылки на следующую страницу, которое будет отправлено, когда поддерживается функция следующей страницы. (См. Таблицу 28-6). Содержание определено в 28.2.3.4. При включении питания этот регистр должен содержать значение по умолчанию 2001H, которое указывает на страницу сообщения с кодом сообщения, установленным в нулевое сообщение. Это значение может быть заменено любым действительным кодом сообщения следующей страницы, который устройство желает передать. Запись в этот регистр должна установить для mr_next_page_loaded значение true.

Взгляд на 10G Ethernet со стороны FPGA разработчика

Многие специалисты знают, что топовое сетевое оборудование использует специальные чипы для обработки трафика. Я принимаю участие в разработке таких молотилок и хочу поделиться своим опытом в создании таких высокопроизводительных девайсов (со интерфейсами 10/40/100G Ethernet).

Для создания нового канала сетевики чаще всего берут оптику, пару SFP+ модулей, втыкают их в девайсы: лампочки радостно загораются, пакеты начинают приходить: чип начинает их передавать получателям. Но как чип получает пакеты из среды передачи? Если интересно, то добро пожаловать под кат.

IEEE 802.3

Ethernet — это стандарт, принятый ассоциацией IEEE. Стандарты 802.3 охватывают все возможные разновидности Ethernet (от 10M до 100G). Сконцентрируемся на конкретной реализации физического уровня: 10GBASE-R («обычный» 10G, без излишеств).

На этом рисунке показаны уровни модели OSI и то, как они отображаются на подуровни протокола Ethernet.

Для каждого типа физического уровня может быть своя реализация отдельных PHY-подуровней: применяется различное кодирование, различные частоты передачи (длины волн), но четкое разделение на уровни везде прослеживается. Наличие независимого от среды интерфейса (XGMII) упрощает разработку прикладной логики чипов, т.к. при любом подключении разработчик где-то получит XGMII. О том, что собой представляет XGMII мы поговорим позже.

Самым близким к среде расположен подуровень PMD: его задачи решают специальные модули, которые хорошо известны сетевым специалистам:

| Тип модуля | Интерфейс |

|---|---|

| XENPAK | XAUI |

| X2 | XAUI |

| XFP | XFI |

| SFP+ | SFI |

В этой таблице уже есть знакомая аббревиатура: XAUI. Оставим рассмотрение XENPAK/X2 на середину статьи, и обратимся к наиболее популярным модулям: XFP и SFP+.

XFI/SFI

XFI и SFI фактически представляют собой один и тот же интерфейс: дифпара, работающая на скоростях от 9.95 до 11.10 гигабод. Набор скоростей обуславливается тем, что несколько стандартов могут использовать этот интерфейс: от 10GBASE-W WAN до 10GBASE-R over G.709. Нас интересует 10GBASE-R LAN с скоростью в 10.3125 гигабод. Одна дифпара используется для приема, другая — для передачи.

XFI/SFI подключается напрямую к ASIC/FPGA

Задачи подуровней PMA и PCS можно решить на чипе, где мы будем выполнять дальнейшую обработку Ethernet пакетов (после того, как выделим их из XGMII). Напомню, что в подуровне PMA необходимо на приеме выделить тактовую частоту и десериализовать входной сигнал. Такую работу могут выполнить специальные аппаратные блоки, которые для других задач нельзя использовать. Эти блоки называются трансиверами. На их подробное описание может уйти целая статья: кому интересно, могут посмотреть посмотреть блок-схему трансиверов в FPGA компании Altera.

После десериализации, данные попадают в подуровень PCS, где производится дескремблирование и декодирование (64b/66b) и отдаются данные в виде XGMII в сторону MAC’a. На передаче выполняются обратные действия.

PCS может быть реализован как с использованием специальных аппаратных блоков (Hard PCS), так и с помощью логики, доступной пользователю (Soft PCS). Разумеется, это утверждение справедливо только для FPGA: в ASIC’ах всё сделанно аппаратно. Производители FPGA закладывают аппаратные PCS блоки для стандартных протоколов, экономя разработчику время и ресурсы FPGA. Наличие таких блоков очень подкупает, т.к. многие стандартные протоколы по опыту работают из коробки, и для большинства из них код предоставляется бесплатно производителем FPGA.

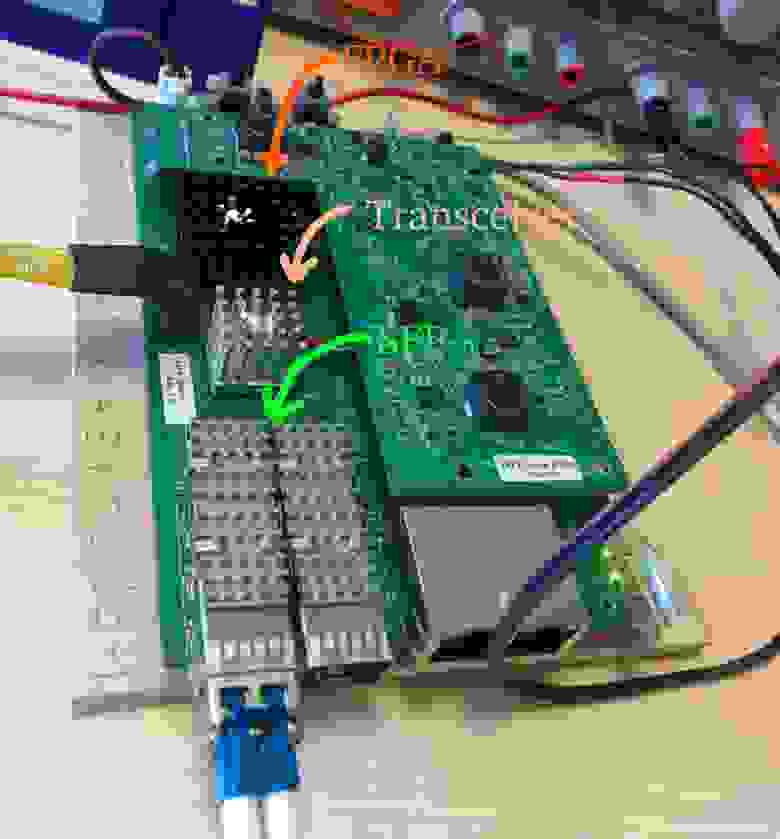

Подключение через внешний чип-трансивер

Трансиверы в FPGA — вещь дорогая, дополнительный десяток трансиверов может значительно поднять цену на чип. Есть более дешевые чипы, с трансиверами, работающими на меньших скоростях (могут сериализовать/десериализовать данные на меньших частотах). Другим высокочастотным интерфейсом, который определен в секции 4 стандарта 802.3, является XAUI: 4 дифференциальные пары с скоростью передачи в 3.125 гигабод (для одной линии передачи).

При использовании XAUI возникает опциональный уровень XGXS, который позволяет отдалить PHY и MAC друг от друга на расстояние. Например, выполнять в разных чипах.

Задачу PMA и PCS в таком подключении могут выполнить специальные 10G трансиверы (Допускаю, что может возникнуть путаница, т.к. чуть ранее «трансиверы» вспыли в FPGA, и теперь тут возникает этот термин. Между прочим, модули XFP/SFP+ тоже называются трансиверами.)

Некоторые PHY-трансиверы могут сразу выдавать на пины интерфейс XGMII и тогда трансиверы в ASIC/FPGA не надо использовать:

Подключение XENPAK/X2

Как я и обещал, мы добрались до этих типов модулей. Несложно увидеть, что их подключение сводится ко второму варианту, только без использования внешнего чипа-трансивера. Модуль возьмет на себя задачи подуровней PMD, PMA и PCS.

XGMII

XGMII определяется в clause 46 стандарта 802.3. Этот интерфейс состоит из независимого приема и передачи. Каждое из направлений имеет 32-битную шину данных (RXD/TXD [31:0]), четыре контрольных сигнала (RXC/TXC [3:0]) и клок, по которому работает направление (RX_CLK/TX_CLK). В стандарте определено, что шины данных и контрольных сигналов анализируются на каждый фронт клока (DDR). По шине данных идёт сам пакет, контрольные сигналы определяют начало помогают «выделять» начало и конец пакета, а так же сообщают об авариях.

300 МГц могут себе позволить только топовые (читай, дорогие) FPGA.

Чаще всего такое ядро реализуется на логике, которая доступна для пользовательских задач. Однако, есть производитель FPGA, который MAC-ядра реализовал аппаратно, экономя ресуры пользователю.

MAC-ядро, выделив пакет из XGMII и разместив пакет во внутренней памяти чипа, «передает» контроль над пакетом прикладной логике чипа: парсерам, фильтрам, системам коммутации и пр. К примеру, если чип стоит на сетевой карте и будет принято решение о том, что надо пакет переслать на хост, то он может быть отправлен с помощью PCIe в оперативную память, подключенную к CPU.

Личный опыт

С L1 в большей степени приходится сталкиваться инженерам-схемотехникам, которые разводят платы для приборов. FPGA-программисты с этим работают только в начале подъема железа: когда заработал XGMII и все трансиверы прошли тесты, то мы концентрируемся на том, как сделать обработку трафика. В одном приборе сделано подключение по первому варианту: SFI напрямую заходит в FPGA. В двух других по второму варианту (с использованием трансивера и XAUI). Так же есть девайс у которого есть подключение как напрямую SFI, так и через XAUI, но без трансивера (FPGA подключается к другому чипу).

Для использования внешних трансиверов (да и вообще, большинства специализированных чипов) необходимо подписать NDA. С этим особых проблем чаще всего не возникает. Вместе с NDA выдаются различные доки, например, настройки регистров чипа. Из опыта работы с трансиверами от двух разных производителей замечу, что при подъеме железа в первой партии стабильно возникают какие-то проблемы с настройкой трансивера, которые относительно быстро решались: трансиверы многофункциональные и иногда для настройки на необходимый режим работы надо пошаманить. Иногда бывает, что документация на чипы бывает очень плохая, и приходиться перебирать разные варианты, а техподдержка не отвечает или открыто заявляет, что поддержку по этим чипам она не осуществляет.

Один из плюсов использования чипа-трансивера является то, что вместе с документацией может распространяться набор прошивок-настроек, которые необходимо загружать в трансивер при установке определенного типа модуля. На сколько я понимаю, эти прошивки производят хитрую настройку эквалайзеров, без которой определенный тип модулей будет работать с битовыми ошибками. Один из таких SFP+ модулей (с лимитирующим усилителем) лечился именно таким образом. Если подключаться без трансивера, то такие настройки надо готовить самим для ASIC/FPGA, что может быть нетривиальной задачей.

Наличие интерфейса, который независим от среды передачи, очень упрощает жизнь, т.к. код (application logic: парсеры, генераторы, анализаторы, фильтры, и пр.) очень легко портировать из старых проектов в новые, т.к. не важно, какой тип подключения использовался.

Подключение (и обработка) 40G/100G к ASIC/FPGA похожа на 10G, однако, там есть свои нюансы. Если будет интересно, этому можно будет посвятить отдельную статью, правда, большой она не будет.

Hello, habr!

Возьмем обычный UDP-пакет с строчкой «Hello, habr!» и отправим на прибор, что бы посмотреть, как он будет выглядеть на XGMII.

У меня на столе лежит разобранный девайс, на котором чаще всего происходит тестирование новых фич: используем его для наглядного примера. Для этого подготовим специальную прошивку и подключим отладчик, чтобы увидеть сигналы внутри чипа. Подключение 10G сделано по второму варианту: с помощью внешнего трансивера, который отдает данные по XAUI в сторону FPGA. Этот трансивер двухканальный: может работать с двумя SFP+.

Как выглядит XGMII (и наш пакет) внутри FPGA:

В этом приборе внутри FPGA используется 72 битная шина XGMII, работающая на по положительному фронту частоты 156.25 МГц.

Спасибо за уделенное время и внимание! Если появились вопросы, задавайте без сомнений.