pll синтезатор что это

Синтезатор частоты PLL Учебник

— Введение или учебник, основам фазовой автоподстройки частоты, работа PLL синтезатор частоты и дизайн

PLL синтезаторы частот широко используются во всех формах Радиостанции сегодня.

Эти синтезаторы частот находятся в разнообразных предметов от сотовых телефонов для всех форм беспроводных продуктов и бытовых радиоприемников и телевизоров к профессиональной радиочастотного оборудования, например, генераторы сигналов и анализаторов спектра, а также профессионального оборудования радио и многое другое.

PLL синтезаторы частоты предлагают очень много преимуществ по сравнению с использованием других форм генератора.

С учетом всех их преимуществах, PLL синтезаторы частот, как правило, предпочтительной формой радиочастотного генератора для большинства приложений. Соответственно синтезаторы включены во многие радио чип-множеств из сотовых телефонов до радио и телевизоров.

PLL Основы

Большинство синтезаторы частот основаны вокруг фазовой автоподстройки частоты или PLL.The PLL использует идею сравнения фаз в качестве основы своей деятельности. Из блок-схемы основного контура, показанного ниже, можно видеть, что существуют три основных схемные блоки, фазовый компаратор, генератор, управляемый напряжением, и контурный фильтр. Опорный генератор иногда входит в блок-схеме, хотя это не является строго частью самого цикла, даже если опорный сигнал требуется для его работы.

Фазовой автоматической подстройки частоты основной диаметр грамм

Фазовой автоматической подстройки частоты, PLL, действует путем сравнения фаз двух сигналов. Сигналы от управляемого напряжением генератора и ссылки ввести фазовый компаратор Здесь третий сигнал равен разности фаз между двумя входными сигналами производится.

Разностный сигнал фаза затем проходит через фильтр контура. Это выполняет ряд функций, включая устранение любых нежелательных продуктов, которые присутствуют на этом сигнале. Как только это было достигнуто оно применяется к управляющим выводом генератора, управляемого напряжением. Эта мелодия напряжение или ошибка напряжения таково, что оно пытается уменьшить ошибку между двумя сигналов, поступающих в фазовый компаратор. Это означает, что генератор, управляемый напряжением потянется к частоте обращения, и когда в замке есть устойчивый напряжение состояние ошибки. Это пропорциональна фазовой ошибки между двумя сигналами, и это константа. Только тогда, когда фаз между двумя сигналами меняется есть разница частота. Как разность фаз остается постоянной, когда цикл находится в замке это означает, что частота генератора, управляемого напряжением точно так же, как ссылки.

PLL Основы синтезатор частоты

Фазовой автоматической подстройки частоты ФАПЧ, необходим дополнительные схемы, если это должно быть преобразовано в синтезатора частоты.

Цикл сломаны и дополнительные блоки добавлены, чтобы обеспечить синтезатора частот действие. Эти блоки добавить смещение частоты в петле в той или иной форме.

Основное действие петли остается. Фазовый детектор вырабатывает напряжение ошибки, пропорциональный разности фаз между двумя входными сигналами. Это означает, что генератор, управляемый напряжением будет работать на другой частоте в том, что из фазового детектора или частоты сравнения.

Есть два основных способа, в котором синтезаторы частот могут быть сделаны из фазовой автоподстройки частоты:

Цифровой PLL синтезатор: Это концепция, которая лежит в основе большинства одиночных синтезаторов петель. Это включает в себя размещение цифровой делитель в петле между генератора, управляемого напряжением. Это означает, что частота генератора, управляемого напряжением будет делится на коэффициент деления делителя, например п, и ГУН будет работать на п раз частоты сравнения фаз. Изменяя коэффициент деления делителя, выходная частота генератора могут быть изменены. Это делает синтезатор частоты программируется.

Основные цифровой синтезатор частоты

Эти цифровые синтезаторы частот идеально подходят для многих приложений самостоятельно. Они выполняют хорошо, где различия между каналами являются относительно высокими. Где могут быть необходимы виртуальные плавной перестройки используя шаги 1 Гц или 10Hz, это требует отношения очень высокого деления, и это может привести к снижению производительности фазового шума и привести к другим вопросам. Для достижения требуемой производительности, оно может пе необходимо объединить цифровой синтезатор ФАПЧ с некоторыми аналоговых методов, как описано ниже.

Аналоговый синтезатор ФАПЧ: Эта форма синтезатора частоты вводит в смеситель ФАПЧ между генератора, управляемого напряжением и фазового детектора. При введении внешнего сигнала в другой терминал смесителя, фиксированное смещение равна внешней частоты, вводится в петлю.

Основные аналоговый синтезатор частоты

Уход необходим при проектировании аналоговые синтезаторы, как могут возникнуть проблемы с сигналом изображения. Хотя фазы для фазового детектора меняются местами, по-прежнему необходимо, чтобы гарантировать, что только правильный сценарий смесь рассматривается системой. Иногда рулевые напряжения могут быть применены к ГУН, чтобы обеспечить правильную работу.

Многие синтезаторы использовать комбинацию обоих этих методов, чтобы иметь возможность производить высокочастотные синтезаторы качества очень рентабельно и с высоким уровнем производительности.

При проектировании синтезатор частот, тщательный анализ требований необходим, особенно характеристики фазового шума, так как это может повлиять на общий дизайн топологии. Это часто может проводиться с использованием компьютерных средств, хотя руководство графический анализ может даже дать некоторые полезные идеи.

Pll синтезатор что это

Перевод даташита Sanyo на микросхему LC72131, LC72131M.

[Обзор]

Микросхемы LC72131 и LC72131M являются синтезаторами частоты с применением PLL (Phase Locked Loop, ФАПЧ, ФАзовая Подстройка Частоты) для использования в тюнерах переносных магнитол и приемников. С помощью этих микросхем легко реализуются быстродействующие тюнеры AM/FM.

[Функциональное описание]

[Назначение выводов]

BO4

8(7)

9(8)

10(9)

2. Состояние портов определяется битами

BO1 может быть выведен сигнал 8 Гц, для этого бит TBC должен быть установлен в 1.

4. Особое внимание нужно уделять выходу

BO1, так как у неё выходное сопротивление больше, чем у

BO4.

5. При подключении питания все порты

BO4 устанавливаются в состояние «разомкнуто».

[Методы последовательного обмена данными]

Микросхемы ФАПЧ и синтезаторы на их основе производства фирмы Analog Devices

Фазовая автоподстройка частоты (ФАПЧ) широко используется в радиотехнических устройствах и системах связи. На основе генераторов, управляемых напряжением (ГУН), и схем ФАПЧ строят синтезаторы частоты, которые позволяют получить сетку стабильных частот. Одним из применений синтезаторов является использование их в качестве опорных генераторов в преобразователях радиочастотных сигналов. В статье рассматриваются принципы ФАПЧ и структура синтезаторов на их основе. Приводятся сведения о микросхемах таких устройств, выпускаемых фирмой Analog Devices.

Фазовая автоподстройка частоты

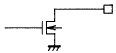

Схема ФАПЧ (английский эквивалент Phase-Locked Loop — PLL) представляет собой систему с контуром обратной связи, который содержит ГУН, фазовый детектор (ФД), фильтр нижних частот (ФНЧ) и усилитель (рис. 1).

ФД (или детектор ошибки) сравнивает фазы сигнала опорного генератора VREF и выходного сигнала ГУН V0 и вырабатывает напряжение V1, величина которого зависит от разности фаз этих сигналов. Если эта разность равна φ радиан, то выходное напряжение ФД будет определяться выражением:

где Kφ — коэффициент передачи «фаза → напряжение ФД» размерностью В/рад.

Выходное напряжение ФД пропускается через ФНЧ для подавления высокочастотных составляющих и их гармоник, которые присутствуют в опорном сигнале и на выходе ГУН. Напряжение с выхода ФНЧ усиливается и используется как управляющее для ГУН (VC). Величина его составляет:

где А — коэффициент усиления усилителя.

Такое управляющее напряжение обеспечивает изменение частоты ГУН по отношению к частоте его собственных колебаний f0 до уровня

где KV — коэффициент передачи «напряжение → частота ГУН» размерностью Гц/В.

Когда осуществлен захват опорного сигнала fОП схемой ФАПЧ, справедливо равенство:

Поскольку согласно (3):

Таким образом, если схема ФАПЧ захватила опорный сигнал, то сдвиг по фазе между этим сигналом и выходным сигналом ГУН устанавливается равным φ, и две частоты fREF и f0 будут точно синхронизированы.

Максимальное напряжение на выходе ФД имеет место при φ = π и φ = 0 и определяется выражением:

Соответствующее максимально возможное управляющее напряжение равно:

В этом случае диапазон частот, который можно обеспечить на выходе ГУН, составляет:

Следовательно, максимальный частотный диапазон сигналов опорного генератора, при которых схема ФАПЧ будет находиться в режиме захвата, составляет:

Величина 2ΔfL называется полосой захвата ФАПЧ и определяется по формуле:

Следует отметить, что полоса захвата симметрична по отношению к частоте собственных колебаний ГУН f0. На рис. 2 приведена зависимость VC от частоты опорного сигнала, характеризующая полосу захвата. Вне этой полосы частота ГУН не может быть синхронизирована с частотой опорного сигнала.

Схемотехника ФАПЧ может быть классифицирована по методу реализации [1].

Если в качестве ФД используется линейный элемент типа четырехквадрантного перемножителя, а остальные элементы контура являются линейными аналоговыми, ФАПЧ называется линейной (linear PLL — LPLL).

Если используется цифровой ФД, а остальные элементы контура ФАПЧ являются линейными аналоговыми, то ФАПЧ называется цифровой (digital PLL — DPLL).

Если ФАПЧ строится исключительно из цифровых блоков, без использования каких-либо пассивных или линейных аналоговых элементов, то ФАПЧ называется полностью цифровой (all digital PLL — ADPLL).

Как и любая цифровая система, полностью цифровая ФАПЧ может быть реализована в виде программы. В этом случае ФАПЧ называется программно реализованной (soft PLL — SPLL).

К основным параметрам ФАПЧ относят фазовый шум, уровень проникновения гармоник опорного сигнала и время захвата.

Фазовый шум порождается малыми флуктуациями случайного характера фазы сигнала опорного генератора. Наличие его на входе ФД приводит к появлению ошибки на его выходе и, как следствие, к нестабильности частоты выходного сигнала ГУН.

Время захвата ФАПЧ это время от момента подачи сигналов на входы ФД до момента возникновения установившегося режима (момента захвата).

Синтезатор частоты с ФАПЧ

Схема ФАПЧ используется в качестве основного элемента при построении синтезаторов частоты, которые вырабатывают сетку высокостабильных частот, кратных частоте опорного генератора. Для обеспечения высокой стабильности используют опорный генератор с кварцевым резонатором. Структура такого синтезатора приведена на рис. 3.

Частота опорного генератора fОП делится на целое число R с помощью входного делителя. На его выходе вырабатывается сигнал с частотой fREF/R. Частота ГУН также делится на целое число N при помощи делителя в петле ФАПЧ, принимая значения f0/N. Когда схема ФАПЧ работает в режиме захвата опорного сигнала, имеет место равенство:

Для получения различных коэффициентов деления применяют программируемые делители. Тем самым обеспечивается широкий спектр выходных частот синтезатора, кратных частоте опорного сигнала. Диапазон выходных частот синтезатора определяется полосой захвата ФАПЧ, а абсолютные значения границ этого диапазона зависят от собственной частоты ГУН, относительно которой располагается полоса захвата (рис. 2). Величина шага изменения частоты синтезатора Δf (разрешающая способность синтезатора) в пределах диапазона его перестройки зависит от величины коэффициента деления делителя N и от времени захвата ФАПЧ. При уменьшении Δf требуется уменьшение времени захвата (времени установления), то есть уменьшение времени перехода от одного устойчивого состояния с частотой f01 до другого устойчивого состояния с частотой f02 = f01±Δf

Уменьшить время захвата можно за счет увеличения полосы пропускания петлевого ФНЧ. Но это приводит к увеличению уровней фазовых шумов и побочных гармоник. При значительном увеличении границы полосы пропускания фильтра (более 0,2(fREF/R)) петля ФАПЧ может стать нестабильной и неспособной к захвату. Для исключения этого необходимый запас по фазе в петле ФАПЧ должен составлять не менее 45°.

Большое значение коэффициента деления N в петле ФАПЧ может повлечь за собой появление некоторых нежелательных эффектов:

В зависимости от значения коэффициента деления N делителя петли ФАПЧ различают ФАПЧ с целочисленным коэффициентом деления (Integer-N PLL) и ФАПЧ с дробным коэффициентом деления (Fractional-N PLL). ФАПЧ с малым временем установления относится к категории быстродействующих (Fast Settling PLL).

Разрешающая способность синтезатора с целочисленным коэффициентом деления N делителя в петле ФАПЧ ограничена величиной fREF/R. При дробном коэффициенте деления N разрешающая способность может составлять доли от величины fREF/R. Другим достоинством систем с дробным коэффициентом деления является уменьшение времени захвата. Например, если fREF/R = 20 МГц и полоса пропускания ФНЧ составляет 150 кГц, то перестройка синтезатора по частоте на 30 МГц будет занимать менее 30 мкс.

В современных синтезаторах время захвата мало, но конечно, что определяется возможностями схемотехники. В ряде случаев, когда требуется повышенное быстродействие системы при переходе от одной частоты к другой, используют два синтезатора: пока один работает на данной частоте в течение времени, большее, чем время захвата, второй синтезатор переключается на другую требуемую частоту. В результате время перехода от одной частоты к другой определяется только временем коммутации выходов синтезаторов.

Микросхемы ФАПЧ производства Analog Devices

Компания Analog Devices выпускает широкий спектр микросхем (МС) ФАПЧ и синтезаторов на основе ФАПЧ. МС ФАПЧ содержат детектор ошибки и два делителя (R и N) с программируемыми коэффициентами деления и ориентированы на применение в схемах высокостабильных перестраиваемых генераторов, устройствах синхронизации и синтезаторах при использовании внешних генераторов (опорного и ГУН) и петлевого ФНЧ. По-видимому, это дало разработчикам основание называть такие микросхемы синтезаторами (PLL Synthesizer), что, вообще говоря, не вполне корректно. Программирование делителей осуществляется, как правило, через единый интерфейс.

Номенклатура МС ФАПЧ по данным на конец 2005 года [3] приведена в таблице 1. Устройства различаются по частотным диапазонам сигналов опорного генератора и ГУН, уровню фазовых шумов и типу делителей в петле ФАПЧ (N), а также по входу опорного генератора (R). Кроме того, выпускаются микросхемы двухканальных ФАПЧ, которые приведены в таблице 2. В промышленно выпускаемых микросхемах используется цифровой детектор ошибки () с выходом по току, где выходной генератор реализован в виде зарядовой помпы (charge pump — CP). Упрощенная схема такого PFD приведена на рис. 4.

Подобная реализация PFD обладает рядом преимуществ по сравнению с классическим детектором с выходом по напряжению: большая линейность, низкая стоимость.

ADF4001 относится к категории низкочастотных ФАПЧ и предназначена для работы в схемах тактовых генераторов с ФАПЧ, работающих в диапазоне до 200 МГц. Делители с программируемыми целочисленными коэффициентами деления (R = 1–16383 и N = 1–8191) позволяют получить широчайший спектр выходных частот на выходе внешнего ГУН.

На рис. 5 приведен пример применения МС ADF4001 в схеме трехчастотного генератора синхронизированных тактовых сигналов.

На этой схеме опорный генератор обозначен как Master Clock, а ГУН — как VCXO — ГУН с кварцевым резонатором.

ADF4007 классифицируется производителем как высокочастотный делитель и синтезатор частоты. Максимальное значение частоты ГУН определяется величиной 7,5 ГГц. Однако коэффициент деления делителя петли ФАПЧ ограничен конечным набором значений N = 8, 16, 32, 64, а входной делитель имеет фиксированный коэффициент деления R = 2. Фазовый шум существенно ниже, чем у ADF4001 и составляет всего –219 дБм/Гц.

ADF4110/4111/4123/4113 — семейство МС, реализованных по единой структурной схеме (рис. 6) и различающихся частотным диапазоном применяемого ГУН (табл. 1). Диапазон допустимых частот опорного генератора у всех микросхем одинаков и составляет 5–104 МГц.

Отличительной особенностью схемотехники данных МС является петлевой делитель, который реализован по схеме, приведенной на рис. 7.

Данная схема содержит предварительный делитель частоты (prescaler), свойства которого определяются двухкоэффициентным параметром Р/(Р+1). Величина этого параметра устанавливается равной 8/9 (Р = 8), 16/17 (Р = 16), 32/33 (Р = 32) или 64/65 (Р = 64). Эти значения определяются условием синхронизации с частотой (4/5)f0. Коэффициенты деления счетчиков A и B могут принимать значения в пределах: А = 0–63, В = 3–8191. Результирующий коэффициент деления определяется соотношением: N = BP + A. В результате диапазон целых значений N существенно расширяется.

Предварительный делитель работает при значении выходной частоты не более 200 МГц. Имеется опция установки режима работы зарядовой помпы.

Микросхемы данного семейства по выводам совместимы с ADF4001.

ADF4106/4107 имеют аналогичную с предыдущими МС структуру (рис. 6). Они отличаются более высокой частотой применяемого ГУН и, соответственно, большей частотой опорного генератора, а также меньшим напряжением питания (табл. 1). Предварительный делитель работает при значении выходной частоты не более 325 МГц.

ADF4116/ADF4117/ADF4118 — семейство, реализованное по сходной с предыдущими МС структуре. Отличие заключается в отсутствии опции установки режима зарядовой помпы. Параметр предварительного делителя составляет Р/(Р+1) = 8/9 для ADF4116 и Р/(Р+1) = 32/33 для ADF4117/4118. Коэффициенты деления счетчиков A и B могут принимать значения в пределах 0–31 и 3–8191 соответственно. Данные МС характеризуются меньшим током потребления.

ADF4153 открывает серию МС с дробным коэффициентом деления делителя в петле ФАПЧ, который повышает разрешающую способность ФАПЧ по частоте. Структурная схема приведена на рис. 8.

Петлевой делитель реализован по схеме рис. 9.

Коэффициент деления такого делителя определяется тремя устанавливаемыми параметрами INT, MOD и FRAC, которые для данной реализации могут принимать значения 31–511, 2–4095 и 0–(MOD–1) соответственно. Результирующий коэффициент дробного делителя петли ФАПЧ определяется соотношением:

Дополнительно разрешающая способность повышается за счет включения переключаемого умножителя (doubler — D) с коэффициентом D, который равен 0 или 1 на входе делителя R (рис. 8). Результирующий коэффициент деления входного делителя RIN получается равным:

где величина R для данного варианта схемы может принимать значения в пределах 1–15.

Данная МС совместима по выводам с ADF4110/4111/4112/4113 и ADF4106. Имеет опцию установки режима работы зарядовой помпы.

ADF4154 в целом аналогична ADF4153 за тем исключением, что в данном случае предварительный делитель делителя петли ФАПЧ имеет только два значения устанавливаемого параметра: 4/5 и 8/9. Совместима по выводам с ADF4110/4111/4112/4113/4106 и ADF4153.

ADF4156 представляет собой дальнейшее развитие МС ADF4154 для работы с ГУН с максимальной частотой до 6 ГГц. В конце 2005 года была выпущена только опытная серия таких микросхем. Подробной информации в виде data sheets на момент подготовки статьи к печати на сайте компании не было. Основные параметры МС приведены в таблице 1.

ADF4193. Новая быстродействующая МС ФАПЧ с дробным петлевым делителем. Архитектура МС, приведенная на рис. 10, специально разработана под стандарты базовых станций мобильных систем связи GSM и EDGE.

МС отличает высокая точность установки фазы выходного сигнала ГУН: среднеквадратическая ошибка фазы составляет всего 0,5° на частоте 2 ГГц. Отличительной особенностью схемотехники МС является включение в схему входного делителя (помимо делителя R и коммутируемого умножителя D) дополнительного делителя T, применение которого позволяет вдвое увеличить частоту опорного генератора. Результирующий коэффициент деления входного делителя RIN получается равным

где D равно 0 или 1, R лежит в диапазоне 1–15, T — 0 или 1.

Кроме того, в схему введен дополнительный ОУ, позволяющий, например, преобразовать симметричный выход зарядовой помпы в несимметричный.

ADF4112L открывает серию двухканальных ФАПЧ, номенклатура которых приведена в таблице 2. Структурная схема этой МС приведена на рис. 11. Двухканальные ФАПЧ имеют, как правило, единый вход от опорного генератора (fREF), но различаются по каналам диапазонами частот допустимых к применению ГУН. Эти частоты обозначают fRF (канал RF) и fIF (канал IF). Кроме того, различие заключается в типе петлевых делителей каналов ФАПЧ. В данной МС оба делителя — дробные, реализованные по схеме рис. 7, а их параметры соответствуют параметрам делителя МС ADF4116/4117/4118.

ADF4217L/ADF4218L/ADF4219L представляют собой семейство двухканальных ФАПЧ с дробными петлевыми делителями, структура и параметры которых идентичны ADF4112L. Основные параметры микросхем приведены в таблице 2. Структура микросхем семейства в целом аналогична ADF4112L (рис. 11). Отличительные особенности схемотехники в доступном виде отсутствуют. В целом микросхемы данного семейства относятся к категории малопотребляющих и рекомендуются к применению в мобильной аппаратуре.

ADF4252 представляет собой сдвоенную ФАПЧ и имеет различные типы петлевых делителей в двух каналах: целочисленный делитель в канале IF и дробный делитель в канале RF (рис. 12). Целочисленный делитель канала IF реализован по схеме рис. 7 и имеет коэффициент деления в пределах от 1 до 32 767. Дробный делитель канала RF реализован по схеме рис. 9 и характеризуется следующими параметрами: INT от 31 до 255, MOD от 2 до 4095, FRAC от 0 до (MOD–1).

Оба канала микросхемы работают от одного источника опорного сигнала и имеют одинаковую структуру входных целочисленных делителей (как в МС ADF4193), но параметры этих делителей разные: RRF от 1 до 15, RIF от 1 до 32 767, D — 0 или 1.

Микросхемы синтезаторов частоты с ФАПЧ от Analog Devices

Синтезаторы частоты с ФАПЧ представлены семейством из 9 микросхем ADF4360-0/1/2/3/4/5/6/7/8 (табл. 3), реализованных по единой структурной схеме (рис. 13).

Схема синтезатора содержит встроенный ГУН, цифровой детектор, выполненный на основе фазового компаратора и зарядовой помпы (см. рис. 4), входной делитель с целочисленным коэффициентом деления R (1–16 383) и петлевой делитель также с целочисленным коэффициентом деления, реализованный по схеме рис. 7. Параметры последнего: Р — 8, 16, 32 и 64; А от 0 до 31, В от 3 до 8191. Схема требует подключения внешнего генератора опорного сигнала с максимальной частотой 250 МГц. Максимальная выходная частота детектора составляет 8 МГц. Напряжение питания всех микросхем однополярное и составляет 3,0–3,6 В. Для уменьшения энергопотребления имеется возможность программируемой установки величины потребляемого тока.

Все микросхемы семейства выпускаются в корпусе LPSCP-24. Микросхемы моделей 0/1/2/3/4/5/6 содержат встроенные индуктивности резонансной системы ГУН. Модели 7/8 требуют подключения внешних индуктивностей, для чего предусмотрены соответствующие выводы. Микросхемы семейства различаются только диапазоном сетки выходных частот (табл. 3).

Программные средства разработки

Компания Analog Devices совместно с Applied Radio Labs разработала программу ADIsimPLL для моделирования ФАПЧ и схем на ее основе. Программа содержит библиотеку моделей выпускаемых микросхем ФАПЧ, а также библиотеку моделей популярных схем ГУН, включая ГУН с кварцевой стабилизацией. ADIsimPLL позволяет проектировать петлевые фильтры различной конфигурации, моделировать шумы ГУН, опорного генератора, петли ФАПЧ, воздействие помех и процесс захвата частоты. По окончании процедуры моделирования может быть получен эскизный вариант топологии печатной платы проектируемого устройства. Программа находится в свободном доступе на сайте Analog Devices [4].

Помимо этого, для моделирования ФАПЧ и схем на их основе разработчик может использовать широко известный пакет MathLab (предпочтительно в версии не ниже 6.5).