perr generation что это

SERR# Generation

материал № 10580

— ошибка четности на фазе адреса транзакции,

— ошибка четности на этапе данных транзакции специального цикла,

— серьезные проблемы, кроме четности, обнаруженные устройством PCI,

— критические сбои системы, обнаруженные логикой системной платы

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

КОММЕНТАРИИ к «SERR# Generation»

ДРУГИЕ МАТЕРИАЛЫ ПО ТЕМЕ

Проявления неисправностей, связанных с данным параметром (0)

IT-WIKI (0)

Параметры BIOS (29)

Описание значений параметров:

Описание значений параметров:

Описание значений параметров:

Параметр включает поддержку ASPM для южного моста материнской платы.

Базовая спецификация PCI Express определяет два уровня ASPM, которые предназначены для обеспечения возможности компенсировать повышенное энергосбережение с быстрым восстановлением до состояния L0.

Описание значений параметров:

— Serial Port Settings

— COM Port Settings

— Onboard UART 1/2

— Onboard UART

— Onboard Serial Port

— Change Settings

Описание значений параметров:

— Serial Port

— COM Port

Описание значений параметров:

— Power Up On PCI/PCIE Devices

— Resume by PCIE PME

— PCI Express PME

Описание значений параметров:

PERR# является устойчивым сигналом трех состояний, используемым для сигнализации об обнаружении ошибки четности, связанной с фазой данных. Во время каждой фазы данных транзакции чтения целевой объект передает данные на шину AD. Таким образом, цель состоит в том, чтобы обеспечить правильную четность для инициатора по сигналу PAR, начинающемуся через один такт после подтверждения TRDY# (Target Ready). По завершении каждой фазы данных инициатор обязан зафиксировать содержимое AD (31: 0] и C/BE # [3: 0] и рассчитать ожидаемый паритет в течение тактового цикла, сразу после завершения фазы данных. Затем инициатор фиксирует бит четности, предоставленный целью, из сигнала PAR на следующем переднем фронте тактовых импульсов и сравнивает вычисленную и фактическую четность. Если происходит несовпадение, инициатор затем устанавливает PERR# в течение следующих тактовых импульсов (если это можно сделать с помощью единицы в бите ответа об ошибке четности в его регистре команд.) Утверждение PERR # откладывает завершение каждой фазы данных на два тактовых цикла PCI.

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

PCIEX16_1 Link Speed

материал № 9681

Параметр устанавливает скорость работы шины расширения PCI Express.

Существует несколько стандартов шины, обеспечивающих возрастающую от поколения к поколению пропускную способность: PCIe Gen 1, PCIe Gen 2, PCIe Gen 3, PCIe Gen 4 и т.д. Указанные стандарты обеспечивают теоретическую пропускную способность в 4, 8, 16, 32 Гб/сек при задействовании 16-ти линий.

КОММЕНТАРИИ к «PCIEX16_1 Link Speed»

ДРУГИЕ МАТЕРИАЛЫ ПО ТЕМЕ

Проявления неисправностей, связанных с данным параметром (0)

IT-WIKI (0)

Параметры BIOS (29)

Описание значений параметров:

Описание значений параметров:

Описание значений параметров:

Параметр включает поддержку ASPM для южного моста материнской платы.

Базовая спецификация PCI Express определяет два уровня ASPM, которые предназначены для обеспечения возможности компенсировать повышенное энергосбережение с быстрым восстановлением до состояния L0.

Описание значений параметров:

— ошибка четности на фазе адреса транзакции,

— ошибка четности на этапе данных транзакции специального цикла,

— серьезные проблемы, кроме четности, обнаруженные устройством PCI,

— критические сбои системы, обнаруженные логикой системной платы

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

— Serial Port Settings

— COM Port Settings

— Onboard UART 1/2

— Onboard UART

— Onboard Serial Port

— Change Settings

Описание значений параметров:

— Serial Port

— COM Port

Описание значений параметров:

— Power Up On PCI/PCIE Devices

— Resume by PCIE PME

— PCI Express PME

Описание значений параметров:

PERR# является устойчивым сигналом трех состояний, используемым для сигнализации об обнаружении ошибки четности, связанной с фазой данных. Во время каждой фазы данных транзакции чтения целевой объект передает данные на шину AD. Таким образом, цель состоит в том, чтобы обеспечить правильную четность для инициатора по сигналу PAR, начинающемуся через один такт после подтверждения TRDY# (Target Ready). По завершении каждой фазы данных инициатор обязан зафиксировать содержимое AD (31: 0] и C/BE # [3: 0] и рассчитать ожидаемый паритет в течение тактового цикла, сразу после завершения фазы данных. Затем инициатор фиксирует бит четности, предоставленный целью, из сигнала PAR на следующем переднем фронте тактовых импульсов и сравнивает вычисленную и фактическую четность. Если происходит несовпадение, инициатор затем устанавливает PERR# в течение следующих тактовых импульсов (если это можно сделать с помощью единицы в бите ответа об ошибке четности в его регистре команд.) Утверждение PERR # откладывает завершение каждой фазы данных на два тактовых цикла PCI.

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

Serial (COM) Port

материал № 11781

КОММЕНТАРИИ к «Serial (COM) Port»

ДРУГИЕ МАТЕРИАЛЫ ПО ТЕМЕ

Проявления неисправностей, связанных с данным параметром (0)

IT-WIKI (3)

ID материала: 7919 / Дата публикации: 27.06.2018 / Просмотров: 186

ID материала: 7871 / Дата публикации: 27.06.2018 / Просмотров: 162

ID материала: 11833 / Дата публикации: 14.01.2018 / Просмотров: 148

Команда, вызывающая консоль управления компьютером в операционной системе Windows.

Открыть консоль можно, если щелкнуть ПКМ по иконке «Компьютер» (Windows 7) или «Этот компьютер» (Win 8, 8.1, 10, находим через проводник) и выбрать пункт меню «Управление«.

Параметры BIOS (37)

Описание значений параметров:

Описание значений параметров:

Описание значений параметров:

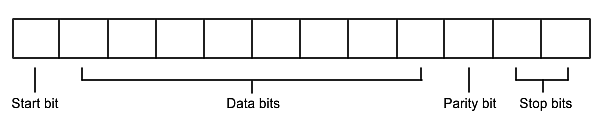

Устанавливает количество стоповых битов. Стоповый бит устанавливается в конце каждого передаваемого символа, обозначая окончание его битовой последовательности для управляемого компьютера (адресата). Таким образом обеспечивается синхронизация процесса приема-передачи данных между двумя сторонами.

Помимо стоповых битов используются также и стартовые биты, обозначающие начало передачи символа (пакета).

Структура пакета данных, передаваемых через COM-порт.

Описание значений параметров:

Параметр включает поддержку ASPM для южного моста материнской платы.

Базовая спецификация PCI Express определяет два уровня ASPM, которые предназначены для обеспечения возможности компенсировать повышенное энергосбережение с быстрым восстановлением до состояния L0.

Описание значений параметров:

— ошибка четности на фазе адреса транзакции,

— ошибка четности на этапе данных транзакции специального цикла,

— серьезные проблемы, кроме четности, обнаруженные устройством PCI,

— критические сбои системы, обнаруженные логикой системной платы

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

Раздел параметров, отвечающих за перенаправление ввода с клавиатуры на последовательный порт (COM-порт).

Данная функция используется для удаленного администрирования других компьютеров (серверов). С управляющего компьютера, где включено перенаправление, сигналы нажатия на клавиши поступают на COM-порт, который соединен COM-кабелем с таким же портом на управляемом компьютере, который воспринимает поступающие команды.

Данная технология удаленного администрирования широко применялась в 1990-х годах.

— Serial Port Settings

— COM Port Settings

— Onboard UART 1/2

— Onboard UART

— Onboard Serial Port

— Change Settings

Описание значений параметров:

— Power Up On PCI/PCIE Devices

— Resume by PCIE PME

— PCI Express PME

Описание значений параметров:

PERR# является устойчивым сигналом трех состояний, используемым для сигнализации об обнаружении ошибки четности, связанной с фазой данных. Во время каждой фазы данных транзакции чтения целевой объект передает данные на шину AD. Таким образом, цель состоит в том, чтобы обеспечить правильную четность для инициатора по сигналу PAR, начинающемуся через один такт после подтверждения TRDY# (Target Ready). По завершении каждой фазы данных инициатор обязан зафиксировать содержимое AD (31: 0] и C/BE # [3: 0] и рассчитать ожидаемый паритет в течение тактового цикла, сразу после завершения фазы данных. Затем инициатор фиксирует бит четности, предоставленный целью, из сигнала PAR на следующем переднем фронте тактовых импульсов и сравнивает вычисленную и фактическую четность. Если происходит несовпадение, инициатор затем устанавливает PERR# в течение следующих тактовых импульсов (если это можно сделать с помощью единицы в бите ответа об ошибке четности в его регистре команд.) Утверждение PERR # откладывает завершение каждой фазы данных на два тактовых цикла PCI.

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

Intel XHCI Mode

материал № 9701

КОММЕНТАРИИ к «Intel XHCI Mode»

ДРУГИЕ МАТЕРИАЛЫ ПО ТЕМЕ

Проявления неисправностей, связанных с данным параметром (0)

IT-WIKI (0)

Параметры BIOS (29)

Описание значений параметров:

Описание значений параметров:

Описание значений параметров:

Параметр включает поддержку ASPM для южного моста материнской платы.

Базовая спецификация PCI Express определяет два уровня ASPM, которые предназначены для обеспечения возможности компенсировать повышенное энергосбережение с быстрым восстановлением до состояния L0.

Описание значений параметров:

— ошибка четности на фазе адреса транзакции,

— ошибка четности на этапе данных транзакции специального цикла,

— серьезные проблемы, кроме четности, обнаруженные устройством PCI,

— критические сбои системы, обнаруженные логикой системной платы

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

— Serial Port Settings

— COM Port Settings

— Onboard UART 1/2

— Onboard UART

— Onboard Serial Port

— Change Settings

Описание значений параметров:

— Serial Port

— COM Port

Описание значений параметров:

— Power Up On PCI/PCIE Devices

— Resume by PCIE PME

— PCI Express PME

Описание значений параметров:

PERR# является устойчивым сигналом трех состояний, используемым для сигнализации об обнаружении ошибки четности, связанной с фазой данных. Во время каждой фазы данных транзакции чтения целевой объект передает данные на шину AD. Таким образом, цель состоит в том, чтобы обеспечить правильную четность для инициатора по сигналу PAR, начинающемуся через один такт после подтверждения TRDY# (Target Ready). По завершении каждой фазы данных инициатор обязан зафиксировать содержимое AD (31: 0] и C/BE # [3: 0] и рассчитать ожидаемый паритет в течение тактового цикла, сразу после завершения фазы данных. Затем инициатор фиксирует бит четности, предоставленный целью, из сигнала PAR на следующем переднем фронте тактовых импульсов и сравнивает вычисленную и фактическую четность. Если происходит несовпадение, инициатор затем устанавливает PERR# в течение следующих тактовых импульсов (если это можно сделать с помощью единицы в бите ответа об ошибке четности в его регистре команд.) Утверждение PERR # откладывает завершение каждой фазы данных на два тактовых цикла PCI.

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

Parallel (LPT) Port Mode

материал № 11786

Назначение параметра: Параметр устанавливает режим работы LPT-порта.

КОММЕНТАРИИ к «Parallel (LPT) Port Mode»

ДРУГИЕ МАТЕРИАЛЫ ПО ТЕМЕ

Проявления неисправностей, связанных с данным параметром (0)

IT-WIKI (0)

Параметры BIOS (29)

Описание значений параметров:

Описание значений параметров:

Описание значений параметров:

Параметр включает поддержку ASPM для южного моста материнской платы.

Базовая спецификация PCI Express определяет два уровня ASPM, которые предназначены для обеспечения возможности компенсировать повышенное энергосбережение с быстрым восстановлением до состояния L0.

Описание значений параметров:

— ошибка четности на фазе адреса транзакции,

— ошибка четности на этапе данных транзакции специального цикла,

— серьезные проблемы, кроме четности, обнаруженные устройством PCI,

— критические сбои системы, обнаруженные логикой системной платы

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

— Serial Port Settings

— COM Port Settings

— Onboard UART 1/2

— Onboard UART

— Onboard Serial Port

— Change Settings

Описание значений параметров:

— Serial Port

— COM Port

Описание значений параметров:

— Power Up On PCI/PCIE Devices

— Resume by PCIE PME

— PCI Express PME

Описание значений параметров:

PERR# является устойчивым сигналом трех состояний, используемым для сигнализации об обнаружении ошибки четности, связанной с фазой данных. Во время каждой фазы данных транзакции чтения целевой объект передает данные на шину AD. Таким образом, цель состоит в том, чтобы обеспечить правильную четность для инициатора по сигналу PAR, начинающемуся через один такт после подтверждения TRDY# (Target Ready). По завершении каждой фазы данных инициатор обязан зафиксировать содержимое AD (31: 0] и C/BE # [3: 0] и рассчитать ожидаемый паритет в течение тактового цикла, сразу после завершения фазы данных. Затем инициатор фиксирует бит четности, предоставленный целью, из сигнала PAR на следующем переднем фронте тактовых импульсов и сравнивает вычисленную и фактическую четность. Если происходит несовпадение, инициатор затем устанавливает PERR# в течение следующих тактовых импульсов (если это можно сделать с помощью единицы в бите ответа об ошибке четности в его регистре команд.) Утверждение PERR # откладывает завершение каждой фазы данных на два тактовых цикла PCI.

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров: