pci serr generation в биосе что это

SERR# Generation

материал № 10580

— ошибка четности на фазе адреса транзакции,

— ошибка четности на этапе данных транзакции специального цикла,

— серьезные проблемы, кроме четности, обнаруженные устройством PCI,

— критические сбои системы, обнаруженные логикой системной платы

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

КОММЕНТАРИИ к «SERR# Generation»

ДРУГИЕ МАТЕРИАЛЫ ПО ТЕМЕ

Проявления неисправностей, связанных с данным параметром (0)

IT-WIKI (0)

Параметры BIOS (29)

Описание значений параметров:

Описание значений параметров:

Описание значений параметров:

Параметр включает поддержку ASPM для южного моста материнской платы.

Базовая спецификация PCI Express определяет два уровня ASPM, которые предназначены для обеспечения возможности компенсировать повышенное энергосбережение с быстрым восстановлением до состояния L0.

Описание значений параметров:

— Serial Port Settings

— COM Port Settings

— Onboard UART 1/2

— Onboard UART

— Onboard Serial Port

— Change Settings

Описание значений параметров:

— Serial Port

— COM Port

Описание значений параметров:

— Power Up On PCI/PCIE Devices

— Resume by PCIE PME

— PCI Express PME

Описание значений параметров:

PERR# является устойчивым сигналом трех состояний, используемым для сигнализации об обнаружении ошибки четности, связанной с фазой данных. Во время каждой фазы данных транзакции чтения целевой объект передает данные на шину AD. Таким образом, цель состоит в том, чтобы обеспечить правильную четность для инициатора по сигналу PAR, начинающемуся через один такт после подтверждения TRDY# (Target Ready). По завершении каждой фазы данных инициатор обязан зафиксировать содержимое AD (31: 0] и C/BE # [3: 0] и рассчитать ожидаемый паритет в течение тактового цикла, сразу после завершения фазы данных. Затем инициатор фиксирует бит четности, предоставленный целью, из сигнала PAR на следующем переднем фронте тактовых импульсов и сравнивает вычисленную и фактическую четность. Если происходит несовпадение, инициатор затем устанавливает PERR# в течение следующих тактовых импульсов (если это можно сделать с помощью единицы в бите ответа об ошибке четности в его регистре команд.) Утверждение PERR # откладывает завершение каждой фазы данных на два тактовых цикла PCI.

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

Serial (COM) Port

материал № 11781

КОММЕНТАРИИ к «Serial (COM) Port»

ДРУГИЕ МАТЕРИАЛЫ ПО ТЕМЕ

Проявления неисправностей, связанных с данным параметром (0)

IT-WIKI (3)

ID материала: 7919 / Дата публикации: 27.06.2018 / Просмотров: 186

ID материала: 7871 / Дата публикации: 27.06.2018 / Просмотров: 162

ID материала: 11833 / Дата публикации: 14.01.2018 / Просмотров: 148

Команда, вызывающая консоль управления компьютером в операционной системе Windows.

Открыть консоль можно, если щелкнуть ПКМ по иконке «Компьютер» (Windows 7) или «Этот компьютер» (Win 8, 8.1, 10, находим через проводник) и выбрать пункт меню «Управление«.

Параметры BIOS (37)

Описание значений параметров:

Описание значений параметров:

Описание значений параметров:

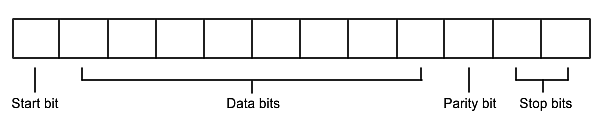

Устанавливает количество стоповых битов. Стоповый бит устанавливается в конце каждого передаваемого символа, обозначая окончание его битовой последовательности для управляемого компьютера (адресата). Таким образом обеспечивается синхронизация процесса приема-передачи данных между двумя сторонами.

Помимо стоповых битов используются также и стартовые биты, обозначающие начало передачи символа (пакета).

Структура пакета данных, передаваемых через COM-порт.

Описание значений параметров:

Параметр включает поддержку ASPM для южного моста материнской платы.

Базовая спецификация PCI Express определяет два уровня ASPM, которые предназначены для обеспечения возможности компенсировать повышенное энергосбережение с быстрым восстановлением до состояния L0.

Описание значений параметров:

— ошибка четности на фазе адреса транзакции,

— ошибка четности на этапе данных транзакции специального цикла,

— серьезные проблемы, кроме четности, обнаруженные устройством PCI,

— критические сбои системы, обнаруженные логикой системной платы

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

Раздел параметров, отвечающих за перенаправление ввода с клавиатуры на последовательный порт (COM-порт).

Данная функция используется для удаленного администрирования других компьютеров (серверов). С управляющего компьютера, где включено перенаправление, сигналы нажатия на клавиши поступают на COM-порт, который соединен COM-кабелем с таким же портом на управляемом компьютере, который воспринимает поступающие команды.

Данная технология удаленного администрирования широко применялась в 1990-х годах.

— Serial Port Settings

— COM Port Settings

— Onboard UART 1/2

— Onboard UART

— Onboard Serial Port

— Change Settings

Описание значений параметров:

— Power Up On PCI/PCIE Devices

— Resume by PCIE PME

— PCI Express PME

Описание значений параметров:

PERR# является устойчивым сигналом трех состояний, используемым для сигнализации об обнаружении ошибки четности, связанной с фазой данных. Во время каждой фазы данных транзакции чтения целевой объект передает данные на шину AD. Таким образом, цель состоит в том, чтобы обеспечить правильную четность для инициатора по сигналу PAR, начинающемуся через один такт после подтверждения TRDY# (Target Ready). По завершении каждой фазы данных инициатор обязан зафиксировать содержимое AD (31: 0] и C/BE # [3: 0] и рассчитать ожидаемый паритет в течение тактового цикла, сразу после завершения фазы данных. Затем инициатор фиксирует бит четности, предоставленный целью, из сигнала PAR на следующем переднем фронте тактовых импульсов и сравнивает вычисленную и фактическую четность. Если происходит несовпадение, инициатор затем устанавливает PERR# в течение следующих тактовых импульсов (если это можно сделать с помощью единицы в бите ответа об ошибке четности в его регистре команд.) Утверждение PERR # откладывает завершение каждой фазы данных на два тактовых цикла PCI.

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

Intel XHCI Mode

материал № 9701

КОММЕНТАРИИ к «Intel XHCI Mode»

ДРУГИЕ МАТЕРИАЛЫ ПО ТЕМЕ

Проявления неисправностей, связанных с данным параметром (0)

IT-WIKI (0)

Параметры BIOS (29)

Описание значений параметров:

Описание значений параметров:

Описание значений параметров:

Параметр включает поддержку ASPM для южного моста материнской платы.

Базовая спецификация PCI Express определяет два уровня ASPM, которые предназначены для обеспечения возможности компенсировать повышенное энергосбережение с быстрым восстановлением до состояния L0.

Описание значений параметров:

— ошибка четности на фазе адреса транзакции,

— ошибка четности на этапе данных транзакции специального цикла,

— серьезные проблемы, кроме четности, обнаруженные устройством PCI,

— критические сбои системы, обнаруженные логикой системной платы

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

— Serial Port Settings

— COM Port Settings

— Onboard UART 1/2

— Onboard UART

— Onboard Serial Port

— Change Settings

Описание значений параметров:

— Serial Port

— COM Port

Описание значений параметров:

— Power Up On PCI/PCIE Devices

— Resume by PCIE PME

— PCI Express PME

Описание значений параметров:

PERR# является устойчивым сигналом трех состояний, используемым для сигнализации об обнаружении ошибки четности, связанной с фазой данных. Во время каждой фазы данных транзакции чтения целевой объект передает данные на шину AD. Таким образом, цель состоит в том, чтобы обеспечить правильную четность для инициатора по сигналу PAR, начинающемуся через один такт после подтверждения TRDY# (Target Ready). По завершении каждой фазы данных инициатор обязан зафиксировать содержимое AD (31: 0] и C/BE # [3: 0] и рассчитать ожидаемый паритет в течение тактового цикла, сразу после завершения фазы данных. Затем инициатор фиксирует бит четности, предоставленный целью, из сигнала PAR на следующем переднем фронте тактовых импульсов и сравнивает вычисленную и фактическую четность. Если происходит несовпадение, инициатор затем устанавливает PERR# в течение следующих тактовых импульсов (если это можно сделать с помощью единицы в бите ответа об ошибке четности в его регистре команд.) Утверждение PERR # откладывает завершение каждой фазы данных на два тактовых цикла PCI.

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

PCI Latency Timer

материал № 11108

Назначение параметра: Параметр, устанавливающий время (в количестве тактов системной шины), в течении которого плата расширения (контроллер, сетевая карта и другие), установленная в PCI-разъем, может занимать PCI-шину для своей работы.

Чем больше задержка, тем эффективнее плата расшерения использует PCI-шину для своей работы, но тем дольше ожидают другие PCI-устройства (если они есть) в компьютере своей очереди.

При настройке данного параметра можно использовать программы для проверки скорости работы плат, подключенных к PCI-шине, чтобы подобрать оптимальный уровень задержки.

КОММЕНТАРИИ к «PCI Latency Timer»

ДРУГИЕ МАТЕРИАЛЫ ПО ТЕМЕ

Проявления неисправностей, связанных с данным параметром (0)

IT-WIKI (0)

Параметры BIOS (29)

Описание значений параметров:

Описание значений параметров:

Описание значений параметров:

Параметр включает поддержку ASPM для южного моста материнской платы.

Базовая спецификация PCI Express определяет два уровня ASPM, которые предназначены для обеспечения возможности компенсировать повышенное энергосбережение с быстрым восстановлением до состояния L0.

Описание значений параметров:

— ошибка четности на фазе адреса транзакции,

— ошибка четности на этапе данных транзакции специального цикла,

— серьезные проблемы, кроме четности, обнаруженные устройством PCI,

— критические сбои системы, обнаруженные логикой системной платы

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

— Serial Port Settings

— COM Port Settings

— Onboard UART 1/2

— Onboard UART

— Onboard Serial Port

— Change Settings

Описание значений параметров:

— Serial Port

— COM Port

Описание значений параметров:

— Power Up On PCI/PCIE Devices

— Resume by PCIE PME

— PCI Express PME

Описание значений параметров:

PERR# является устойчивым сигналом трех состояний, используемым для сигнализации об обнаружении ошибки четности, связанной с фазой данных. Во время каждой фазы данных транзакции чтения целевой объект передает данные на шину AD. Таким образом, цель состоит в том, чтобы обеспечить правильную четность для инициатора по сигналу PAR, начинающемуся через один такт после подтверждения TRDY# (Target Ready). По завершении каждой фазы данных инициатор обязан зафиксировать содержимое AD (31: 0] и C/BE # [3: 0] и рассчитать ожидаемый паритет в течение тактового цикла, сразу после завершения фазы данных. Затем инициатор фиксирует бит четности, предоставленный целью, из сигнала PAR на следующем переднем фронте тактовых импульсов и сравнивает вычисленную и фактическую четность. Если происходит несовпадение, инициатор затем устанавливает PERR# в течение следующих тактовых импульсов (если это можно сделать с помощью единицы в бите ответа об ошибке четности в его регистре команд.) Утверждение PERR # откладывает завершение каждой фазы данных на два тактовых цикла PCI.

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

PCI и PCI-X

Прерывания PCI: INTx#, PME#, MSI и SERR#

Сигнализация событий управления энергопотреблением — PME#

Линия PME#, введенная в PCI 2.0, служит для сигнализации в системе управления энергопотреблением PM (Power Management): смены состояния устройств, генерации пробуждения системы по событию. Эта линия электрически доступна всем устройствам PCI; как и линии INTx#, PME# никак не обрабатывается мостами, а лишь доводится до всех абонентов. Логика сигнализации аналогична INTx#: устройство сигнализирует о событии, замыкая линию PME# на «землю», таким образом, сигналы о событиях логически собираются по функции ИЛИ. Обработчик этого прерывания может выявить устройство, подавшее сигнал, путем программных обращений к конфигурационным регистрам всех устройств, способных к генерации этого сигнала. Устройства (функции), имеющие отношение к управлению энергопотреблением, имеют в конфигурационном пространстве структуру с идентификатором Capability и набор регистров:

Подробности управления энергопотреблением в PCI и форматы соответствующих конфигурационных регистров приведены в PCI PM 1.1.

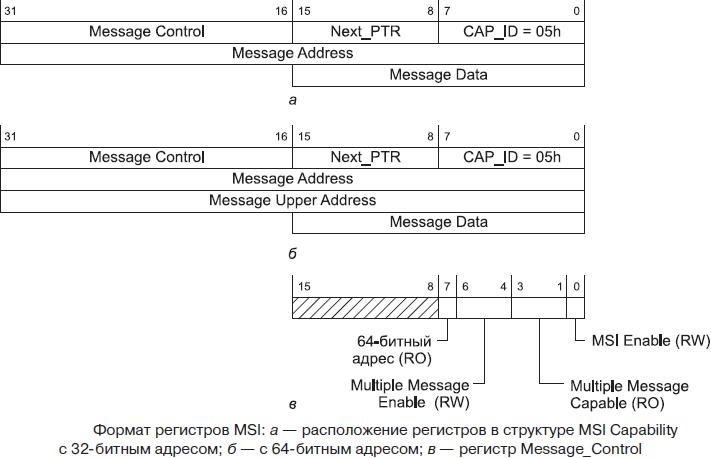

Прерывания сообщениями — MSI

На шине PCI имеется прогрессивный механизм оповещения об асинхронных событиях, основанный на передаче сообщений MSI (Message Signaled Interrupts). Здесь для сигнализации запроса прерывания устройство запрашивает управление шиной и, получив его, посылает сообщение. Сообщение выглядит как обычная запись двойного слова в ячейку памяти, адрес (32-битный или 64-битный) и шаблон сообщения на этапе конфигурирования устройств записываются в конфигурационные регистры устройства (точнее, функции). В сообщении старшие 16 бит всегда нулевые, а младшие 16 бит несут информацию об источнике прерывания. Устройство (функция) могут нуждаться в сигнализации нескольких типов запросов; в соответствии с его потребностями и своими возможностями система указывает устройству (функции), сколько различных типов запросов оно может вырабатывать.

Возможность использования MSI описывается в конфигурационном пространстве структурой MSI Capability (CAP_ID = 05h), которая должна присутствовать в пространстве каждой функции, поддерживающей MSI. В структуре имеется 3 или 4 регистра (см. рисунок ниже):

По аппаратному сбросу MSI запрещен; его можно разрешить программно установкой бита MSI Enable (после программирования адреса и шаблона сообщения), и тогда генерация прерываний по линиям INTx# запрещается. Самая «богатая» прерываниями функция (для которой Multiple Message Enable = 101) при записи сообщения идентифицирует конкретное условие прерывания (одно из 32 возможных) по линиям AD[4:0].

Отметим, что быстрая посылка подряд двух и более одинаковых сообщений может быть воспринята системой как одно прерывание (из-за низкой реактивности). Если требуется обработка каждого из них, обработчик должен обеспечивать уведомление устройства, а оно не должно посылать следующее сообщение до получения уведомления, чтобы прерывания не терялись. Различающиеся сообщения друг другу не мешают.

Прерывания через MSI позволяют избежать бед разделяемости, обусловленной дефицитом линий запросов прерывания в PC. Кроме того, они решают проблему целостности данных: все данные, записываемые устройством до посылки MSI, дойдут до получателя гарантированно раньше начала обработки MSI. Прерывания через MSI от одних устройств в одной системе могут использоваться наряду с обычными INTx# от других устройств. Но каждое устройство (функция), использующее MSI, не должно использовать прерывания через линии INTx#.

Механизм MSI может использоваться на системных платах, имеющих «продвинутый» контроллер прерываний APIC. Правда, конкретная реализация поддержки MSI может потенциальные возможности облегчения идентификации большого числа запросов прерывания свести лишь к увеличению числа доступных запросов прерываний (и используемых ими векторов). Так, например, для системных плат на чипсетах с хабом ICH2 и ICH3 фирмы Intel поддержка MSI сводится к организации альтернативных путей подачи запросов IRQ[1:23] на входы APIC (запросы IRQ с номерами 0, 2, 8 и 13 через MSI не передаются). Всем устройствам PCI назначается один и тот же адрес сообщений (Message Address = FEC00020h), по которому в APIC находится регистр IRQ Pin assertion. В сообщении используются лишь младшие 5 бит, в которых указывается номер взводимого запроса прерывания в диапазоне 1–23 (исключая 2, 8 и 13). Линии запросов, используемые в MSI, программируются на чувствительность к перепаду (сообщения имитируют только фронт сигнала). По этой причине прерывания с номерами, используемыми в MSI, не могут использоваться совместно (разделяемо) с прерываниями, полученными другими способами (по линиям запросов от устройств PCI и от других устройств системной платы). Возможно, что в других платформах прерывания через MSI используются более эффективно.